# High-level Methods for OBDD-based Sequential Verification

Dissertation zur Erlangung des Doktorgrades der Naturwissenschaften

vorgelegt beim Fachbereich IV der Universität Trier

von

Dipl. Inform. Christian Stangier

2002

1. Berichterstatter: Prof. Dr. Christoph Meinel (Universität Trier)

2. Berichterstatter: Prof. Dr. Werner Damm (Carl von Ossietzky Universität Oldenburg)

Datum der Disputation: 29. November 2002

# Contents

| In | Introduction 1 |                   |                                                     |    |  |  |

|----|----------------|-------------------|-----------------------------------------------------|----|--|--|

| 1  | $\mathbf{Pre}$ | limina            | ries                                                | 7  |  |  |

|    | 1.1            | Boolean Functions |                                                     |    |  |  |

|    |                | 1.1.1             | Operations on Boolean Functions                     | 7  |  |  |

|    |                | 1.1.2             | Data Structures for Boolean Functions               | 8  |  |  |

|    | 1.2            | OBDI              | Os – Ordered Binary Decision Diagrams               | 8  |  |  |

|    |                | 1.2.1             | Manipulation of OBDDs                               | 10 |  |  |

|    |                | 1.2.2             | Efficient Synthesis of OBDDs                        | 10 |  |  |

|    |                | 1.2.3             | Influence of the Variable Order on the OBDD-Size    | 12 |  |  |

|    |                | 1.2.4             | Optimization of the Variable Order                  | 13 |  |  |

|    |                | 1.2.5             | Sifting                                             | 14 |  |  |

|    | 1.3            | Verific           | cation of Combinatorial Circuits                    | 14 |  |  |

|    | 1.4            | Forma             | al Verification of Sequential Systems               | 15 |  |  |

|    |                | 1.4.1             | Equivalence Check for Two Finite State Machines     | 15 |  |  |

|    |                | 1.4.2             | Reachability Analysis                               | 16 |  |  |

|    |                | 1.4.3             | Symbolic Model Checking                             | 18 |  |  |

|    | 1.5            | Softwa            | are Packages                                        | 20 |  |  |

| 2  | <b>A C</b>     | Case St           | tudy in Formal Verification                         | 23 |  |  |

|    | 2.1            | Forma             | al Verification in an Industrial Setting            | 23 |  |  |

|    |                | 2.1.1             | Protocol Compiler                                   | 24 |  |  |

|    | 2.2            | An As             | ssertion Checking Methodology for Protocol Compiler | 24 |  |  |

|    |                | 2.2.1             | Verification Flow                                   | 25 |  |  |

|    |                | 2.2.2             | Example RS232                                       | 25 |  |  |

|    |                | 2.2.3             | Example Cow-Stomach                                 | 28 |  |  |

|    |                | 2.2.4             | Dealing with Inputs during Verification             | 31 |  |  |

|    | 2.3            | Concl             | usion and Open Problems                             | 33 |  |  |

ii *CONTENTS*

| 3 | 3 Partitioning |                  |                                                     |    |  |  |  |  |  |

|---|----------------|------------------|-----------------------------------------------------|----|--|--|--|--|--|

|   | 3.1            | The Pa           | artitioning Problem                                 | 35 |  |  |  |  |  |

|   |                | 3.1.1            | Common Partitioning Strategy                        | 36 |  |  |  |  |  |

|   |                | 3.1.2            | Related Work                                        | 38 |  |  |  |  |  |

|   | 3.2            | RTL P            | artitioning                                         | 39 |  |  |  |  |  |

|   |                | 3.2.1            | Hardware Description Languages                      | 39 |  |  |  |  |  |

|   |                | 3.2.2            | RTL based Partitioning Heuristic                    | 39 |  |  |  |  |  |

|   |                | 3.2.3            | Discussion of the Method                            | 41 |  |  |  |  |  |

|   |                | 3.2.4            | Experimental Results                                | 42 |  |  |  |  |  |

|   | 3.3            | Group            | Partitioning                                        | 48 |  |  |  |  |  |

|   |                | 3.3.1            | Dependency Matrices                                 | 48 |  |  |  |  |  |

|   |                | 3.3.2            | The Grouping Algorithm                              | 48 |  |  |  |  |  |

|   |                | 3.3.3            | Reordering of Clusters                              | 51 |  |  |  |  |  |

|   |                | 3.3.4            | Experimental Results                                | 53 |  |  |  |  |  |

| 4 | Hie            | ierarchization 5 |                                                     |    |  |  |  |  |  |

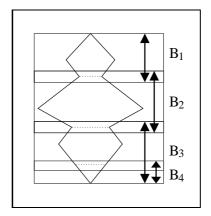

|   | 4.1            | Hierard          | chical Image Computation                            | 57 |  |  |  |  |  |

|   |                | 4.1.1            | Hierarchical Partitioning                           | 58 |  |  |  |  |  |

|   |                | 4.1.2            | Hierarchical Image Computation                      | 60 |  |  |  |  |  |

|   | 4.2            | Dynam            | ic Conjunction Scheduling                           | 62 |  |  |  |  |  |

|   |                | 4.2.1            | Dynamic Scheduling Heuristic                        | 62 |  |  |  |  |  |

|   |                | 4.2.2            | Experimental Results                                | 64 |  |  |  |  |  |

|   | 4.3            | Hierard          | chical Group Partitioning                           | 67 |  |  |  |  |  |

|   |                | 4.3.1            | Discussion of the AndExist Algorithm                | 67 |  |  |  |  |  |

|   |                |                  | Modular Grouping of the Transition Relation         |    |  |  |  |  |  |

|   |                | 4.3.3            | Experimental Results                                | 72 |  |  |  |  |  |

|   | 4.4            | Conclu           | sion                                                | 76 |  |  |  |  |  |

| 5 | Rec            | ordering         | 5                                                   | 77 |  |  |  |  |  |

|   | 5.1            | Sample           | e Sifting                                           | 78 |  |  |  |  |  |

|   |                |                  |                                                     | 78 |  |  |  |  |  |

|   |                | 5.1.2            | Sample Sifting Strategy for Symbolic Model Checking | 78 |  |  |  |  |  |

|   |                | 5.1.3            | Experimental Results                                | 85 |  |  |  |  |  |

|   | 5.2            | Block I          | Restricted Sifting                                  | 90 |  |  |  |  |  |

|   |                |                  |                                                     | 90 |  |  |  |  |  |

|   |                | 5.2.2            | BRS Strategy for Symbolic Model Checking            |    |  |  |  |  |  |

|   |                | 5.2.3            | Experimental Results                                |    |  |  |  |  |  |

|   | 5.3            | Conclu           | sion                                                |    |  |  |  |  |  |

| CONTENTS            |     |

|---------------------|-----|

| 6 Conclusion        | 97  |

| A Additional Tables | 99  |

| References          | 107 |

iv CONTENTS

# Introduction

#### Motivation

During the last years we are facing an enormous increase in utilization of digital circuits: Many applications like information processing, telecommunication, network computing, automotive and industrial control demand for even more powerful and faster circuits.

The computer industry keeps pace with this demand by increasing the system integration of VLSI (Very Large Scale Integration) designs. Moore's law [Moo65], which says that the number of transistors on a chip doubles every 18 month is still valid and an end of this growth is not in sight.

On the other hand there is a growing need for proving correctness of complex designs for the following two reasons:

- 1. Simulation is the conventional method for validation of digital designs. This method loses its ability to guarantee correctness, if designs grow larger and become more complex.

- 2. Economic, safety and security reasons request for mathematical (i.e. formal) proofs of the correctness of digital systems.

The famous *Pentium bug*, an error in the floating division unit of the Intel Pentium I processor, which was responsible for a \$475 Million loss in Intel's revenue, shows the importance of proving correctness of digital hardware.

But, there are more important reasons to insist on the correctness of digital circuits than the profit of a company:

- The automotive control of an airplane should be correct under any circumstance.

- The control of a satellite should be at least resettable (there is no way to switch the power off and back on).

- Hardware realizations of cryptographic protocols should be guaranteed to be functionally correct.

Virtually any aspect of our daily live is affected by digital circuits with an increasing tendency and the above list gives only a few examples of possible applications for formal verification.

A central problem in CAD (computer aided design) of digital designs is the representation of Boolean functions. Within the last decade ordered binary decision diagrams (OBDDs) [Bry86] have become one of the most popular data structures in this area.

The classical application for OBDDs is the formal verification of combinatorial circuits. Here, the equivalence of the specification and an implementation of a given circuit has to be checked. Recently, the focus of the interest in research and industry has moved to the application of OBDDs to sequential systems. Many design tools use OBDDs to represent finite state machines. The emerging need for formal verification of sequential systems requires the use of highly sophisticated data structures and algorithms.

## Formal Verification of Sequential Systems

Formal verification is the mathematical proof that an implementation of a circuit C fullfils its specification S. In combinatorial verification this is done by checking the equivalence of the representations of C and S. OBDDs are well suited for this task, because they represent Boolean functions in a compact way and the equivalence check is trivial. The term sequential verification denotes formal verification of synchronous finite state machines (FSMs) or systems of communicating FSMs. Various sequential verification techniques exist, e.g. the functional equivalence of two FSMs can be tested. Unfortunately, often a formal specification S of a FSMs is not given. In this case, certain properties that the FSM should satisfy are tested. These properties include: Assertions, deadlocks, livelocks, etc. The main applications in sequential verification are assertion checking and model checking. [CES86]

A major problem in sequential verification is the so called *state space explosion problem*, resulting from huge state space of complex FSMs that cannot be represented explicitely. This problem can be circumvented by representing state sets symbolically by using OBDDs. Together with the efficient algorithms for manipulation of Boolean functions OBDDs enable efficient *symbolic breadth first traversal* for reachability analysis, assertion checking and symbolic model checking [McM93].

Usage of OBDDs does not solve all problems in sequential verification. The size of the OBDD representation and the efficiency of the algorithms heavily influences the performance of the applications.

Two of the main areas for optimization in OBDD-based sequential verification are

- Partitioning of the transition relation of the FSM to allow efficient reachable states computation, and

- ordering of state- and input-variables to reduce the size of the OBDD-representation.

# Scope of the Thesis

This work covers practical aspects of OBDD-based sequential verification. It is structured in a top-down fashion: We start by presenting a formal verification methodology at the user-level of a design and verification tool. Then, we present algorithms at the application-level of OBDD-based formal verification, i.e. reachability and image computation. Finally, we move down to the representation-level and deal with improvement of the OBDD-representation size.

The mayor area of this work is Algorithmic Engineering.

OBDD-based sequential verification moved into the focus of research for various reasons:

- Designers realize that their simulation based validation approaches are no longer capable to find all bugs and search for more reliable techniques.

- OBDD-based techniques for combinatorial verification are well investigated and one hopes to transfer these techniques to sequential verification.

- OBDDs are already integrated in many design tools simply for function representation purposes, and thus they are ready to use for formal verification.

- The interest in formal verification has generally increased.

Some of the points mentioned above are challenges: Enabling a designer to verify complex properties of a design, requires almost *push-button-technology*. Some of the points actually are problematic: Algorithms that are good in combinatorial verification do not necessary work in sequential verification.

For these reasons we propose the utilization of

#### High-Level Methods

to improve the efficiency and ease the applicability of OBDD-based sequential verification. The main contributions of this work are:

- 1. An assertion checking methodology, integrated in the verification flow of the high-level design and verification tool Protocol Compiler.

- 2. New approaches for partitioning of transition relations of complex finite state machines, that significantly improve the performance of OBDD-based sequential verification.

- 3. Dynamic variable reordering techniques that drastically reduce the time required for reordering without a trade-off in OBDD-size.

#### Overview of the Thesis

The present work is structured as follows:

We start this work in Chapter 1 with recapitulating the basic concepts, state-of-the-art data structures and algorithms and give the most common applications in formal verification in VLSI design.

In Chapter 2 we conduct a case study on formal verification in an industrial setting. We develop a methodology for assertion checking, which is a subproblem of model checking and apply it to two examples: A simplified RS232 transceiver and a pipelined FIFO-like buffer. The study shows how to integrate formal verification into a typical verification flow. The study also shows the limitations of this approach and serves as a motivation for the research presented in the following chapters.

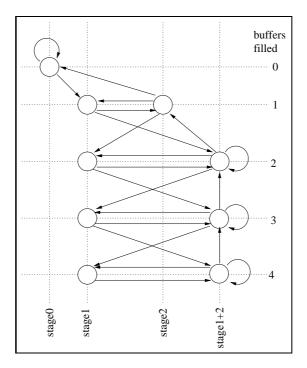

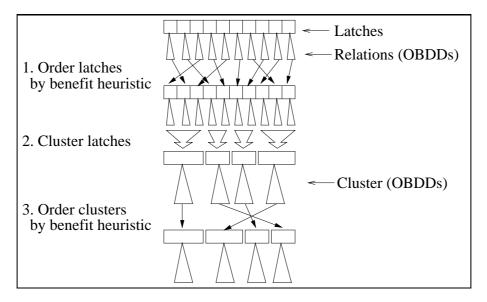

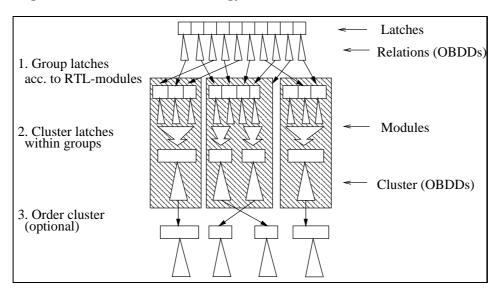

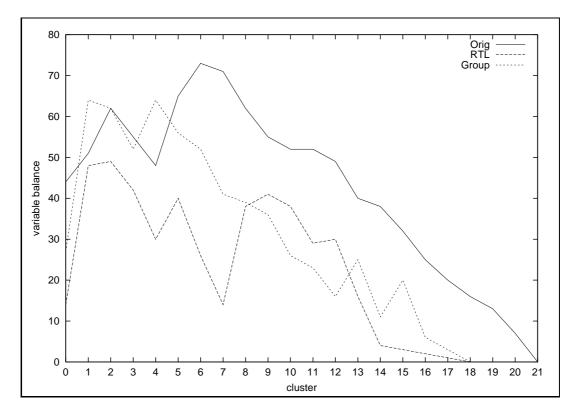

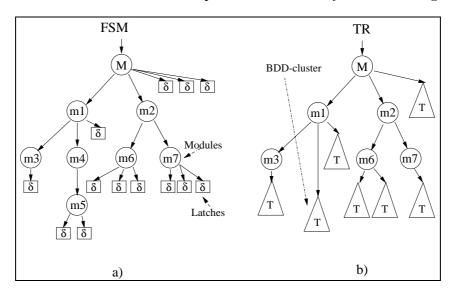

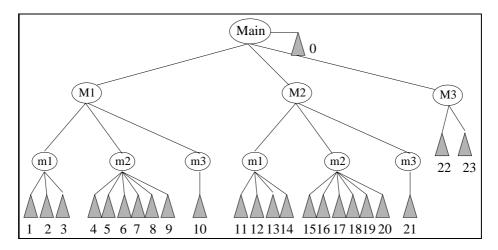

Chapter 3 deals with the partitioning problem, i.e. building a partitioned transition relation of a finite state machine. The transition relation allows image computation, and thus reachable states computation and model checking. We start by presenting a heuristic that uses explicit high-level information of the design under consideration. The heuristic is called

RTL-method, because it utilizes register transfer level (RTL) constructs of the description language Verilog. The outcome is an increased efficiency of the formal verification algorithms.

In the second part of Chapter 3 we develop, motivated by the success of the RTL-method, a heuristic that is independent of high-level information. This heuristic imitates the effects of the RTL-method that cause the improved efficiency. This heuristic is called *Group-method*.

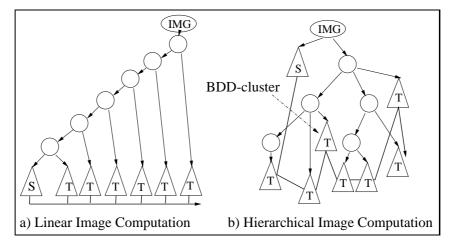

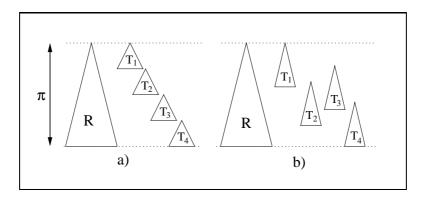

The heuristics presented in Chapter 3 produce a somewhat "flat" partitioning, but nowadays designs are structured – and developed – in a hierarchical fashion. Thus it seems obvious to adapt hierarchy for the partitioning problem. In Chapter 4 we present algorithms that build a hierarchical partitioned transition relation and allow hierarchical image computation. The first heuristic in Chapter 4 for partitioning is based on high-level information and is called due to its modular structure RTLMOD-method. We also tackle another important problem in OBDD-based image computation: The conjunction scheduling problem. We present a conjunction scheduling heuristic that is based on the hierarchical image computation. A highlight of this heuristic is that it is able to change the schedule dynamically.

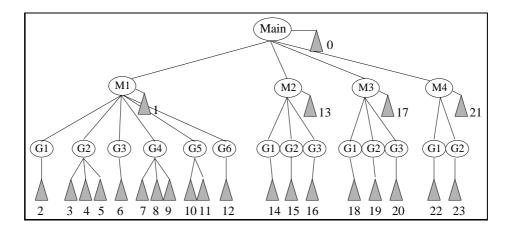

In the second part of Chapter 4 we develop – similar to Chapter 3 – a heuristic that is independent of explicit high-level information. This heuristic is called *GROUPMOD-method*.

In Chapter 5 we focus on a problem on the representation layer of formal verification, i.e. the optimization of the OBDD-representation by dynamic variable reordering.

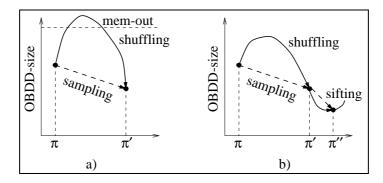

Reordering of variables is the only way to improve the size of the OBDD-representation. In the last years the dynamic Sifting approach turned out to produce the best average results. But, this approach can be very time consuming, and time is the most valuable resource in model checking. We present two acceleration techniques for variable reordering: Sample Sifting for symbolic model checking and Block Restricted Sifting for symbolic model checking. The first method utilizes high-level information of the represented functions and the state of the computation, while the second only is application dependent and thus easier to implement.

Finally, Chapter 6 concludes this thesis with summarizing its key results and an outlook on possible future work.

#### **Publications**

Parts of this thesis have been published in similar form:

- C. Stangier and U. Holtmann: Applying Formal Verification with Protocol Compiler, Proc. of EUROMICRO Digital System Design (DSD'01), 2001.

- Ch. Meinel and C. Stangier: Speeding Up Image Computation by using RTL Information, Proc. of Formal Methods in CAD (FMCAD'00), LNCS 1954, Springer, 2000.

- Ch. Meinel and C. Stangier: A New Partitioning Scheme for Improvement of Image Computation, Proc. of ASP Design Automation Conference (ASPDAC'01), 2001.

- Ch. Meinel and C. Stangier: *Hierarchical Image Computation with Dynamic Conjunction Scheduling*, Proc. of IEEE Int. Conf. on Computer Design, 2001.

- Ch. Meinel and C. Stangier: Modular Partitioning and Dynamic Conjunction Scheduling in Image Computation, In Proc, ACM/IEEE Int. Workshop on Logic and Synthesis, 2002.

Ch. Meinel and C. Stangier: Speeding Up Symbolic Model Checking by Accelerating Dynamic Variable Reordering, Proc. of IEEE 10th Great Lakes Symopsium on VLSI, 2000.

Some parts have been published in a survey paper:

Ch. Meinel and C. Stangier: Data Structures for Boolean Functions. BDDs - Foundations and Applications, In: Computational Discrete Mathematics, Ed. H. Alt, LNCS 2122, Springer, 2001.

## Acknowledgments

First of all, I would like to thank my advisor Prof. Christoph Meinel for all his support and advice over the last years.

Many thanks are devoted to Ulrich Holtmann from Synopsys, who put this thesis on the right track.

I have to thank Harald Sack for always being motivating and listening to all my complaints.

Thanks to my parents for being my parents (and not someone else's parents). And, thanks to Tommy Stumpe, for being a great friend and providing me with vital doses of Rock'n'Roll (in every sense).

Furthermore, I wish to thank all the members of Prof. Meinel's working group, who helped and supported me during my PhD.

# Chapter 1

# **Preliminaries**

This chapter covers the basic concepts that underly this work. In particular we introduce ordered binary decision diagrams (OBDDs), the state-of-the-art data structure for representation of Boolean functions. We discuss properties of OBDDs and present the basic algorithms for manipulation of OBDDs. In the Section 1.4 we introduce the main applications of OBDD-based sequential formal verification, i. e. state space traversal, equivalence checking and symbolic model checking. The chapter is concluded by an description of the software packages we used to implement our algorithms and heuristics.

#### 1.1 Boolean Functions

#### Definition 1.1

- The set  $\{0,1\}$  is denoted by  $\mathbb{B}$ .

- The set of all Boolean functions  $\mathbb{B}^n \to \mathbb{B}, n \in \mathbb{N}$  is denoted by  $\mathbb{B}_n$ .

In computer-aided design, Boolean functions  $f \in \mathbb{B}_n$  are of central importance for describing the switching behavior of digital circuits. Hence, those functions are also called *switching functions*. By introducing a suitable 0-1-encoding, all finite problems can – at least in principle – be modeled by means of switching functions. The great importance of switching functions stems from the possibility to obtain substantially simplified, optimized and with optional properties provided circuits by applying optimization techniques during the design process. In the area of VLSI circuits this task is performed by CAD systems. But, before optimization techniques can be applied, a way to represent the switching functions themselves uniquely and as efficiently as possible in computers has to be found.

The representation of a Boolean function is not an end in itself: On the basis of such a representation the various algorithms of CAD systems are performed. Hence, it is important to analyze the ability of the representation for supporting the basic operations of the algorithms.

#### 1.1.1 Operations on Boolean Functions

The following list gives the basic operations on Boolean functions  $(f, g \in \mathbb{B}_n)$ :

Satisfiability test (SAT): Test, whether there exists an assignment  $a \in \mathbb{B}^n$  of the variables of f with f(a) = 1.

**Equivalence test:** Check, whether  $f \equiv g$  for two functions f, g.

**Evaluation:** Compute f(a) for a given assignment  $a \in \mathbb{B}^n$

**Synthesis:** Compute a representation  $P_h$  of  $h = f \otimes g$  for an arbitrary binary Boolean operator  $\otimes$ .

**Replacement by constants:** Compute a representation  $P_h$  for  $h = f_{|x_i=a|}$  (i. e. the input  $x_i$  in f is replaced by the Boolean constant  $a \in \mathbb{B}$ ).

**Replacement by function:** Compute a representation  $P_h$  for  $h = f_{|x_i=g|}$  (i. e. the input  $x_i$  in f is replaced by the Boolean function g).

**Quantification:** Compute a representation  $P_h$  for  $h = \forall x_i : f$  (universal quantification) resp.  $h = \exists x_i : f$  (existential quantification) of f.

**Minimization:** Given a representation  $P_f$  of a function f. Compute a minimized representation  $P'_f$ .

#### 1.1.2 Data Structures for Boolean Functions

Why are special data structures for the representation of Boolean function needed? Well known representations for Boolean functions include:

**Circuits:** The elementary SAT problem is NP-complete for circuits and the minimization problem is NP-hard.

Boolean formulas: The equivalence test is co-NP-complete for Boolean formulas.

**Truth tables:** All operations can be performed efficiently, but truth tables always require exponential space.

Conjunctive Normal Form (CNF): Even simple functions often have only an exponential representation in CNF. The SAT problem is NP-complete for CNF.

**Disjunctive Normal Form (DNF):** The problems with DNF are similar to CNF, but SAT is in P.

Branching Programs (BPs): Many functions can be represented very efficiently using branching programs but already the SAT problem is NP-complete for BPs.

For definitions of these data structures and proofs of the lower bounds see [MT98]. All these data structures fail for use in electronic design automation either for reasons of space complexity (e.g. truth tables) or time complexity of the operations (e.g. branching programs).

## 1.2 OBDDs – Ordered Binary Decision Diagrams

In 1986, by introducing ordered binary decision diagrams (OBDDs), Randall E. Bryant got ahead a fundamental step in the search for suitable data structures in circuit design [Bry86, Bry92]. Bryant's OBDDs combine two advantages: the new established data structure is not only quite space efficient but can also be handled efficiently from the algorithmic point of view.

**Definition 2.1** An Ordered Binary Decision Diagram (OBDD) P for a Boolean function  $f \in \mathbb{B}_n$  is a directed acyclic graph consisting of inner nodes labeled by Boolean variables and sinks labeled by the Boolean constants 1 and 0. Each inner node has two outgoing edges: the 1-edge and the 0-edge. The OBDD has a starting node called root. The computation of  $f(a_1,\ldots,a_n)$  follows a path from the root to a sink, where on a node labeled by  $x_i$  the input bit  $a_i$  is tested. If  $a_i=1$ , the path follows the 1-edge, otherwise the 0-edge. The value of the reached sink determines the value of  $f(a_1,\ldots,a_n)$ . On a path from the root to the sink, each variable occurs at most once. The variables on a path respect a given order, which is (possibly after renaming)  $x_1,\ldots,x_n$ . For an edge leading from a node labeled by  $x_i$  to a node labeled by  $x_j$  it follows that j>i.

An OBDD with more than one root node (i. e. representing  $f : \mathbb{B}^n \to \mathbb{B}^m$ ,  $m \in \mathbb{N}$ , m > 1) is called a *shared* OBDD [MIY90]. In practice all functions to be represented are kept in one single shared OBDD. For simplicity we stay with the term OBDD.

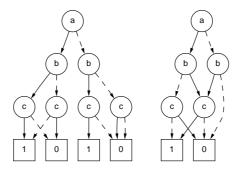

Figure 1.1 gives two examples for OBDDs for the Boolean function  $f = bc + a\overline{b}\overline{c}$  w. r. t. the variable order a < b < c.

Figure 1.1: Two OBDDs representing  $f = bc + a\overline{b}\overline{c}$

From the Shannon decomposition

$$f = x \cdot f_{|x=1} + \overline{x} \cdot f_{|x=0}$$

one can derive the first important property of OBDDs:

**Property 2.2 Universality:** Any Boolean function  $f \in \mathbb{B}_n$  can be represented by an OBDD w.r.t. any predefined variable order  $\pi$ .

For a proof see [SW93].

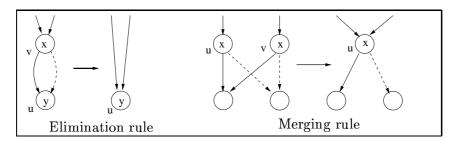

If we give up the restrictions on the variable order and the read-once property we get more general decision diagrams. Like in many other representations general decision diagrams have difficulties in handling Boolean functions caused by the missing uniqueness. By using a surprisingly simple reduction mechanism, for OBDDs this problem can be solved very elegantly. Obviously, the following two reduction rules keep the represented function invariant:

Elimination rule: If 1- and 0-edge of a node v point to the same node u, then eliminate v, and redirect all incoming edges from v to u.

Merging rule: All terminal nodes with a given label are merged to one node, redirect all incoming edges to this node. If the non-terminal nodes u and v are labeled by the same variable, their 1-edges lead to the same node and their 0-edges lead to the same

node, then eliminate one of the two nodes u, v, and redirect all incoming edges to the remaining node.

The elimination rule and the merging rule are illustrated in Figure 1.2.

Figure 1.2: Reduction rules for OBDDs

**Definition 2.3** An OBDD is called reduced, if none of the two reduction rules can be applied.

It is easy to see that the right OBDD in Figure 1.1 is reduced. Regarding the algorithmic properties of reduced OBDDs, the following property of canonicity is of basic importance:

**Property 2.4 Canonicity:** With respect to a fixed variable order  $\pi$ , the reduced OBDD of a Boolean function f is uniquely determined.

For a proof also see [SW93].

Besides universality and canonicity, OBDDs have a third fundamental property, which makes OBDDs such a successful data structure for representation of Boolean functions: It is the efficiency of algorithmic manipulation.

#### 1.2.1 Manipulation of OBDDs

OBDDs are the only data structure for the representation of switching functions, whose representation size is not exponential in the number of variables for all functions (like truth tables) and that has deterministic polynomial time algorithms for all important operations.

In Figure 1.3, the runtime and space requirements for these operations are given ( $|P_f|$  denotes the number of nodes in the OBDD P for the function f, which depends on n variables and  $a \in \{0,1\}^n$ ). All OBDDs have to respect the fixed variable order  $\pi$ . (Results due to [Bry86, SW93])

It is worthwhile mentioning that most operations (except synthesis and replacement by function) have time and space requirements linear in the size of the OBDD. Together with an efficient implementation OBDDs form a powerful data structure.

#### 1.2.2 Efficient Synthesis of OBDDs

By  $\otimes$  we denote an arbitrary binary Boolean operation, e.g. the conjunction or the disjunction. In order to compute the OBDD  $P_h$  of  $h = f \otimes g$  from the OBDD representations

| Operation                                                           | Runtime                  | Space                    |

|---------------------------------------------------------------------|--------------------------|--------------------------|

| Satisfiability test $(\exists a, f(a) = 1)$                         | $O( P_f )$               | $O( P_f )$               |

| Equivalence test $(f \equiv g)$                                     | $O(min( P_f , P_g ))$    | $O( P_f  +  P_g ))$      |

| Evaluation $(f(a))$                                                 | O(n)                     | $O(P_f)$                 |

| Composition $(f \otimes g)$                                         | $O( P_f \cdot  P_g )$    | $O( P_f \cdot P_g )$     |

| Replacement by constant $(f_{x_i=c})$                               | $O( P_f )$               | $O( P_f )$               |

| Replacement by function $(f_{x_i=g})$                               | $O( P_f ^2 \cdot  P_g )$ | $O( P_f ^2 \cdot  P_g )$ |

| Quantification (e.g. $\exists x_i : f = f_{x_i=1} \lor f_{x_i=0}$ ) | $O( P_f ^2)$             | $O( P_f ^2)$             |

| Reduction (minimization of $P_f$ w.r.t. $\pi$                       | $O( P_f )$               | $O( P_f )$               |

Figure 1.3: Complexity of OBDD operations

$P_f$  and  $P_g$  of two functions f and g, one uses Shannon's decomposition w.r.t. the leading variable x in the variable order  $\pi$ :

$$h = f \otimes g = x (f|_{x=1} \otimes g|_{x=1}) + \overline{x} (f|_{x=0} \otimes g|_{x=0}),$$

where  $f|_{x=1}$  is the subfunction that results from f after replacing the variable x by the constant 1. By repeated application of this decomposition, an OBDD representation  $P_h$  of the function h can be computed.

In an OBDD  $P_f$  every node represents a subfunction f' of f. If the node that represents f' is marked with  $x_i$ , its successors represent  $f'|_{x_i=1}$  resp.  $f'|_{x_i=0}$ . For the representation of any subfunction in  $P_h$  two pairs of nodes from  $P_f$  and  $P_g$  have to be computed. If one would simply follow the Shannon decomposition, where the number of computations doubles on each level,  $2^n$  pairs would be computed (for n variables). But, only  $(|P_f| \cdot |P_g|)$  different pairs exist. Thus, re-computation of pairs has to be avoided, as different subfunctions may be represented by the same node.

The already computed results from earlier stages are being recalled from a *computed-table*. In this way, the originally exponential number of decompositions is now bounded by the product of the two OBDD-sizes.

To increase the usage of the computed table all synthesis operations are mapped to a single operation, the so called if-then-else operator (ITE):

$$ITE(f, g, h) = f \cdot g + \overline{f} \cdot h.$$

For example  $h = f \cdot g$  maps to h = ITE(f, g, 0). Because of the huge number of ITE operations during synthesis, the computed table is usually implemented as a hash based cache to reduce memory consumption. The cache exploits the locality of reference, i.e. results are usually only reused shortly after their computation.

Another helpful construction is the usage of a *unique-table* which holds in a hash-table all already represented nodes. Before a node is created it is checked in the unique-table whether an functionally equivalent node already exists. This technique implements the merging rule. Together with an immediate check for the elimination rule the constructed OBDDs are always reduced and there is no need to call the reduction operation explicitly.

#### Remark:

- In a reduced OBDD the complexity for the satisfiability test (SAT) reduces to: O(1), because the 0-function is uniquely represented by the 0-sink.

– In a reduced shared OBDD the complexity for the equivalence test  $(f \equiv g)$  reduces to O(1), because equivalent functions are represented by the same node, i.e. the equivalence test is a pointer comparison.

#### Construction of OBDDs: Symbolic Simulation

The process of constructing an OBDD is called *symbolic simulation* of the circuit to be represented. Symbolic simulation is based on the synthesis operation:

Starting with the (trivial) OBDD representations of the input nodes one constructs, in topological order, OBDDs for each gate from the OBDDs of the corresponding predecessor gates.

Of course, it may happen that the OBDDs of the circuits are quite large. However, many circuits of practical interest inherently contain much structure – hence, the reduction rules of the OBDDs cause the graphs describing the circuit to remain small.

#### 1.2.3 Influence of the Variable Order on the OBDD-Size

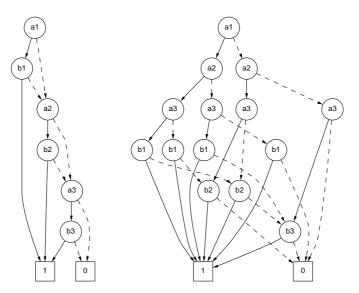

The size of an OBDD and hence the complexity of its manipulation heavily depends on the underlying variable order. An example is shown in Figure 1.4. With respect to the variable order  $a_1, b_1, \ldots, a_n, b_n$  the function

$$a_1b_1 + a_2b_2 + \ldots + a_nb_n$$

has an OBDD representation of linear size. For the variable order  $a_1, a_2, \ldots, a_n, b_1, b_2, \ldots, b_n$  however, the size of the OBDD grows exponentially in n. It can be shown that any order that separates the a-variables from the b-variables leads to an exponentially large OBDD.

Figure 1.4: Influence of the variable order on OBDDs

The same effect occurs in the case of adder functions: Depending on the variable order, the OBDD-size varies from linear to exponential in the number of input bits. Other important functions, e.g. the multiplication of two *n*-bit numbers imply OBDDs of exponential size w.r.t. every variable order [Bry91, Woe01].

Due to the uniqueness of the OBDD representation of a Boolean function f w.r.t. a given variable order, the only way to optimize the size of the OBDD representation for f is to find a suited variable order.

#### 1.2.4 Optimization of the Variable Order

Due to the strong dependency of the OBDD-size upon the chosen variable order it is one of the most important problems in the use of OBDDs to construct "good" orders, i.e. orders that fit well to the represented function. However, the problem to construct an optimal order of a given OBDD is known to be NP-hard [THY93, BW96]. The currently best known exact procedure is based on dynamic programming and has running time  $O(n \cdot 3^n)$  [Weg00]. Unfortunately, for real-life applications this method is useless. To make the problem even worse, Sieling [Sie98] has shown that there is no polynomial time approximation scheme for the variable ordering problem unless P=NP.

We have to distinguish two different approaches for optimization of the variable order:

Static Techniques: There exist a variety of heuristics to determine a variable ordering before building the OBDD of a function. These heuristics utilize various information given by the netlist of the function [MWB88, MIY90, FOH93]. It turned out that these heuristics often work only for very specific functions. Nevertheless, these heuristics can be useful to determine starting orders.

Applications in OBDD-based sequential verification often require representation of state sets, as these states sets and thus their OBDD representation changes, modifications of the variable order become necessary and a dynamic approach is required

**Dynamic Techniques:** Dynamic Variable Reordering is the process of improving the variable order and hence the size of an already existing OBDD.

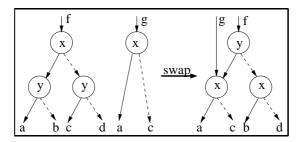

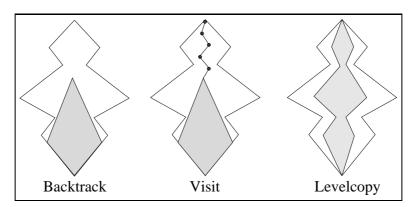

All dynamic variable reordering strategies currently are based on the so called *swap* operation. The swap operation exchanges the position of two neighboring variables in the variable order. The advantage of the swap operation is that it only affects the OBDD-nodes on the two levels that are exchanged. Thus, the operation remains local and its effects on the OBDD-size can be measured immediately. Also, the operation is symmetric and can be reverted at any time. Figure 1.5 shows a schematic of the swap operation, in which the number of nodes could be reduced by one.

Figure 1.5: Schematic of the Swap Operation.

Virtually any optimization paradigm has been applied to variable reordering, but still one of the most successful strategies is the local search algorithm proposed by Rudell 1993.

#### 1.2.5 Sifting

Rudell's so called *Sifting* [Rud93] algorithm is a local search algorithm, based on the swap operation. In its basic form it works as follows (see also Figure 1.6): Each variable consecutively is moved through the variable order by performing repeated swap operations. The best OBDD-size is stored and after the variable order has been moved to the bottom and the top of the variable order it is moved to the stored best position. Because the size of the OBDD may drastically grow during sifting of a variable, a factor *MAXGROWTH* limits the maximum growth of the OBDD-size during sifting of a variable.

The sifting algorithm performs a local search on up to  $n^2$  variable orders (on a OBDD with n variables) out of n! possible variable orders and thus visits only a small fraction of the search space. Nevertheless, in practice the Sifting algorithm produces sufficient results.

```

\begin{aligned} & \textbf{Sifting}(P) \ \{ \\ & \textbf{foreach}(i \in \{1 \dots n\}) \{ \\ & \textbf{optsize} = |P|; \ \textbf{optpos} = \textbf{startpos} = \textbf{i}; \\ & \textbf{for}(j = \textbf{startpos} \ \textbf{to} \ \textbf{n-1}) \{ \\ & \textbf{swap}(P,j+1,j); \\ & \textbf{if}(|P| < \textbf{optsize}) \{ \ \textbf{optsize} = |P|; \ \textbf{optpos} = \textbf{j} \}; \\ & \textbf{if}(|P| > \textbf{optsize} * \textbf{MAXGROWTH}) \ \textbf{break}; \\ & \} \\ & \textbf{for}(k = \textbf{j} \ \textbf{downto} \ 2) \{ \\ & \textbf{swap}(P,k-1,k); \\ & \textbf{if}(|P| < \textbf{optsize}) \{ \ \textbf{optsize} = |P|; \ \textbf{optpos} = \textbf{k} \}; \\ & \textbf{if}(|P| > \textbf{optsize} * \textbf{MAXGROWTH}) \ \textbf{break}; \\ & \} \\ & \textbf{if}(\textbf{optpos} < \textbf{k}) \ \textbf{for}(\textbf{j} = \textbf{k} \ \textbf{downto} \ \textbf{optpos} + 1) \ \textbf{swap}(P,j-1,j); \\ & \textbf{else} \ \textbf{for}(\textbf{j} = \textbf{k} \ \textbf{to} \ \textbf{optpos} - 1) \ \textbf{swap}(P,j+1,j); \\ & \} \\ & \} \end{aligned}

```

Figure 1.6: Basic Sifting Algorithm in Pseudocode

#### 1.3 Verification of Combinatorial Circuits

In our notion combinatorial circuits compute functions  $f: \mathbb{B}_n^m$ ,  $(n, m \in \mathbb{N})$ . They do not contain memory elements like flip-flops or latches. The task in verification of combinatorial circuits is to check whether an implementation of a circuit C fulfills its specification S, i.e. both S and C produce the same functional outputs for all inputs. It can be easily seen that this is an intractable problem if all inputs variations to the circuit are tested explicitly.

OBDD-based combinatorial verification proceeds in two steps:

- 1. Construct the OBDDs  $P_C$  and  $P_S$  for C and S by symbolic simulation.

- 2. Check the equivalence of the OBDDs  $P_C$  and  $P_S$ .

In case of a strong canonical representation, i.e. when both functions are represented within the same OBDD, the equivalence test itself consists of a single pointer comparison. Each step in the iteration can be performed efficiently w.r.t. the OBDD-sizes of the predecessor gates. This shows that the difficulty of the NP-complete equivalent test [GJ78] has now been shifted into the representation size.

If C and S are not equivalent the operation  $P_C \oplus P_S$  gives the inputs where implementation and specification differ. This may be used for debugging.

## 1.4 Formal Verification of Sequential Systems

A task that is more complex than the verification of combinatorial circuits is the verification of sequential or reactive systems. Throughout this thesis we consider only those systems that can be represented by synchronous finite state machines (FSMs) or systems of communicating FSMs.

**Definition 4.1** A Finite State Machine (FSM) M is a six-tuple  $(Q, I, O, \delta, \gamma, q_0)$ , where Q is a set of states, I is the input alphabet, O the output alphabet,  $\delta: Q \times I \to Q$  is the next-state function,  $\gamma: Q \times I \to O$  is the output function, and  $q_0$  is the initial state.

The most common techniques used for formal verification of sequential systems are:

- equivalence check for two finite state machines,

- reachability analysis, including assertion checking, and

- model checking.

#### 1.4.1 Equivalence Check for Two Finite State Machines

A central task in formal verification of sequential systems controllers is the test for equivalence of two given finite state machines. This is needed if correctness of a FSM has to be checked, e.g. after an optimization process.

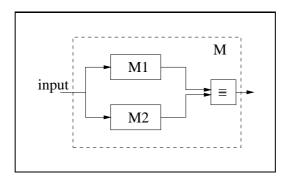

The equivalence test of two finite state machines  $M_1$  and  $M_2$  itself can be reduced to a reachability analysis by using the construction in Figure 1.7: Let M denote the so-called product machine, whose state space is the Cartesian product of the state spaces of  $M_1$  and  $M_2$ . The output of M for a given state and a given input is 1, if and only if for this configuration the outputs of  $M_1$  and  $M_2$  agree.  $M_1$  and  $M_2$  have the same input/output behavior if and only if the output of M evaluates to 1 for all reachable states. Hence, reachability analysis is the key problem.

Figure 1.7: Product machine for FSM verification

#### 1.4.2 Reachability Analysis

The computation of the reachable states is a core task for optimization and verification of sequential systems. As we have seen it is needed for equivalence checking for FSMs, also checking for *error states* or assertion checking requires the computation of the reachable states.

Since the set of reachable states can be quite large, an explicit representation of this set, e. g. in form of a list, usually suffers from the *state space explosion* problem. Coudert, Berthet and Madre have investigated the characteristic function of state sets which can be considered as a Boolean function and therefore be represented by an OBDD [CBM89, CM95]. They have shown that this representation form fits well to the operations, which have to be performed for the computation of the reachable states.

#### Symbolic Representation of FSMs

Typically, the components of a FSM are binary encoded. Let p be the number of input bit, n be the number of state bits and m the number of output bits. Then  $\delta$  is a function  $\delta: \mathbb{B}^n \times \mathbb{B}^p \to \mathbb{B}^n$ ,  $\lambda$  is a function  $\lambda: \mathbb{B}^n \times \mathbb{B}^p \to \mathbb{B}^m$  and  $q_0 \in \mathbb{B}^n$ .

#### Remark:

The problem of encoding the states of an FSM is a hard problem itself, but beyond the focus of this work. For a detailed description of the state encoding problem see e. g. [The98].

If an encoding of the states with n bits is given, we can represent any set of states by an OBDD representing the characteristic function c of this set:

$$c(x) = \sum_{a \in c^1} x_1^{a_1} \cdots x_n^{a_n},$$

where  $a \in \{0,1\}^n$  is an assignment and  $x_i^1 = x_i$  resp.  $x_i^0 = \overline{x_i}$ . Obviously the set operators  $\cap$  and  $\cup$  equal to  $c_1 \cdot c_2$  resp.  $c_1 + c_2$ .

The essential part of OBDD-based traversal techniques is the **transition relation** (TR), which is based on the transition functions. If the states of an FSM M defined according to Definition 1.4.1 are encoded by n bits,  $\delta = (\delta_1, \ldots, \delta_n)$  and the input is encoded by p bits the transition relation of M yields to:

$$TR(x, y, e) = T(x_1, \dots, x_n, y_1, \dots, y_n, e_1, \dots, e_p) = \prod_{1 \le i \le n} (y_i \equiv \delta_i(x, e)),$$

where x denotes the present state, y the next state, and e the input. The TR is used for traversal of the state space.

#### BFS traversal

If the reachable states are computed according to a breadth-first-traversal, the representation via the characteristic function allows to compute all corresponding successor states within a single step. For this reason, one also uses the term  $symbolic\ breadth-first\ traversal$ . Once more, the complexity of the computation depends on the OBDD-size of the occurring state sets.

Figure 1.8 gives an outline of the traversal algorithm. In the first step of the BFS traversal iteration, set To of all successor states of the set From is computed. The image computation

step results in a set depending only on next-state variables y. After renaming the set To is depending on present-state variables x. The set of new states New is computed by subtracting the set of already reached states Reached from the set To. The new states are then added to the reached states. The iteration is repeated until no new states are found.

```

Traverse(TR, S_0) {

/* Transition Relation TR, initial set S_0 */

/* Output: Set of reachable states */

Reached = From = S_0;

do {

To = Img(TR, From);

To = To<sub>Y → X</sub>;

New = To \ Reached;

From = New;

Reached = Reached \cup New;

} while (New \neq \emptyset);

return Reached;

}

```

Figure 1.8: Basic algorithm for reachability analysis based on breadth-first traversal

#### Image computation

The symbolic breadth first reachable states computation mainly consists of repeated image computations Img(TR, From) of a set of already reached states From:

$$Img(TR, From) = \exists_{x,e}(TR(x, y, e) \cdot From)$$

The transition relation is monolithically represented as a single OBDD and such a monolithic representation is usually much too large to allow an efficient computation of the reachable states. Therefore, more sophisticated reachable states computation methods make use of a **partitioned transition relation** [BCL91], i. e. a cluster of OBDDs each of them representing the TR of a subgroup of latches. A transition relation partitioned over sets of latches  $P_1, \ldots, P_j$  can be described as follows:

$$\mathrm{TR}(x,y,e) = \prod_j \mathrm{TR}_j(x,y,e)$$

, where

$$\mathrm{TR}_j(x,y,e) = \prod_{i \in P_j} \delta_i(x,e) \equiv y_i.$$

#### Image computation using AndExist

With the use of a partitioned transition relation the image computation can be iterated over  $P_i$  and the  $\exists$  operation can be applied during the product computation (early quantification):

$$Img(TR, R) = \exists_{nj} (TR_j \cdot \ldots \cdot \exists_{n^2} (TR_2 \cdot \exists_{n^1} (TR_1 \cdot From) \ldots),$$

where  $v^i$  are those variables in  $(x \cup e)$  that do not appear in the following  $TR_k$ ,  $(i < k \le j)$ . The so called AndExist [BCL91] or AndAbstract operation performs the AND operation of two functions (here partitions) while simultaneously applying existential quantification  $(\exists_{x_i} f = (f_{x_i=1} \lor f_{x_i=0}))$  on a given set of variables. The variables to be quantified out are those that are not in the support of the remaining partitions. Unlike the conventional AND operation the AndExist operation only has an exponential upper bound for the size of the resulting OBDD, but for many practical applications it prevents a blow-up of OBDD-size during the image computation.

Another important problem in the context of image computation is finding an optimal schedule of the partitions for the AndExist operation. Geist and Beer [GB94] presented a heuristic for the ordering of partitions each representing a single state variable. The goal of this heuristic is to keep the support variable set of the intermediate products as small as possible. This heuristic was broadened by Ranjan et.al. [Ran95] to allow partitions including more than one state variable.

An insight into the complexity of the partition problem was given by Hojati et.al. [HKB96]: They have shown that finding a tree of conjunctions s.t. the support of the largest intermediate product is less than a given constant is NP-complete even under the simplifying assumption that the support of  $f \wedge g$  is the union of the supports of f and g.

For a more detailed description of OBDD-based reachability analysis see [MT98].

#### 1.4.3 Symbolic Model Checking

Since a complete formal verification of a sequential system is often too complex, methods are of interest that guarantee at least correctness of certain properties. One of them is the so called *model checking*.

Model checking is the problem to decide whether an implementation satisfies its specification given in terms of a temporal logic, e.g. the so called *computation tree logic* (CTL). The formulas of CTL describe properties of infinite paths of states that are traversed during the computation.

The idea to use OBDDs for a symbolic representation of state sets during model checking was first introduced by Burch et. al. [Bur90].

Using this way of symbolic model checking, real-life systems up to  $10^{100}$  states can be verified.

#### The Temporal Logic CTL

The logic that is used in symbolic model checking is a modal logic and it is called *computation tree logic* (CTL). CTL is based on the concept of *branching time*. In branching time the temporal order "<" defines a tree, which branches toward the future. The past of each event is uniquely defined, but its future is not. This corresponds to the dynamic behaviour of FSMs, where the the past sequence of traversed states is unique, but the future states are not known.

The reason to use CTL is that its operators can be easily expressed by fixed point computations. CTL consist only of present and future operators, past operators are not allowed.

In addition to the Boolean operators  $\land$ ,  $\lor$  and  $\neg$ , CTL has four temporal operators:

- X The next operator describes a condition that is true in the next state of the computation.

- **G** The *qlobal* operator describes a condition that is true for all states of a path.

- **F** The future operator describes a condition that is true on a path sometimes in the future.

**U** The *until* operator  $a\mathbf{U}b$  is true on a path if a is true until b is true.

All temporal operators are quantified with either an universal quantifier  $\mathbf{A}$  ("on all paths it holds...") or an existential quantifier  $\mathbf{E}$  ("there exists a path, where...").

Typical examples of CTL formulas of practical relevance include:

- AG( req  $\rightarrow$  AF ack): Each request is eventually acknowledged.

- AG  $\neg$ (p  $\land$  q): Mutual exclusion: p and q are never satisfied at the same time.

- AG EF  $(s_0)$ : There is always a sequence of paths that allow to return to the initial state  $s_0$ . This property checks for deadlocks.

#### Computation of the operands

The operands EX, EU and EG are computed by the routines CheckEX, CheckEU and CheckEG, where the latter two are fixed point computations:

**CheckEX** consists of an pre-image computation:

$$CheckEX(p) = PreImg(TR, p) = \exists y (TR(x, y) \land p).$$

CheckEU computes the least fixed point for EU and can be described inductively as:

$$CheckEU_{0}(p,q,TR) = q$$

$$CheckEU_{i+1}(p,q,TR) = CheckEU_{i}(p,q,TR) \lor$$

$$(p \land CheckEX(CheckEU_{i}(p,q,TR),TR))$$

The number of states represented by the sequence of the  $CheckEU_i$  increases monotonously. The sequence converges and at a certain iteration k, because the number of states is finite:

$$CheckEU_{k+1} = CheckEU_k = CheckEU.$$

CheckEG computes the greatest fixed point for EG and can be described inductively as:

$$CheckEG_0(p,TR) = p$$

$CheckEG_{i+1}(p,TR) = CheckEG_i(p,TR) \land$

$(p \land CheckEX(CheckEG_i(p,TR),TR))$

The number of states represented by the sequence of the  $CheckEG_i$  decreases monotonously. The sequence converges and at a certain iteration k, because the number of states is finite:

$$CheckEG_{k+1} = CheckEG_k = CheckEU.$$

The remaining operators EFp, AXp, AGp and A(p U q) are derived from the above operators by the following rules:

$$\begin{array}{rcl} EFp & = & E(trueUp) \\ AXp & = & \neg EX \neg p \\ A(qUp) & = & \neg (E(\neg pU \neg q \wedge \neg p) \vee EG \neg p) \end{array}$$

Figure 1.9 gives an algorithmic description of the operators CheckEX, CheckEU and CheckEG that form the basic symbolic model checking algorithm Eval(f).

For a more detailed introduction to symbolic model checking see [McM93].

```

Eval(f) {

case{

(f== atomic proposition): return f;

(f== \neg p): return \neg Eval(p);

(f==p \lor q): return Eval(p) \lor Eval(q);

(f==EXp): return EvalEX(p);

(f = E(p U q)): return EvalEU(Eval(p), Eval(q), 0);

(f== EGp): return EvalEG(eval(p),1);

}

EvalEX(p){

return PreImg(TR,p);

EvalEU(p,q,y){

y' = q \lor (p \land evalEX(y));

if (y == y') return y;

else return EvalEU(p,q,y');

EvalEG(p,y){

y'=(p \land EvalEX(y));

if (y == y') return y;

else return EvalEG(p,y');

```

Figure 1.9: Basic Symbolic Model Checking Algorithm

## 1.5 Software Packages

In the following we will briefly describe the OBDD package and the formal verification package, in which we implemented our algorithms and heuristics. The Protocol Compiler synthesis and verification package is described in Chapter 2.

#### The OBDD Package

The Colorado University Decision Diagram Package (CUDD) [Som] is a BDD-package written by Fabio Somenzi and his working group at the University of Colorado at Boulder. It inherits algorithms for OBDDs, zero-suppressed OBDDs (ZDDs) [Min93] and algebraic DDs (ADDs) [BFG93+]. CUDD is written in C, allowing easy programming and fast access of graph data-structures. CUDD includes various algorithms for dynamic reordering like Sifting or Group-sifting. Alternative techniques like simulated annealing [BLW95] or genetic algorithms [DBG95] are implemented as well. CUDD includes sophisticated memory management techniques. We are using version 2.3.0 of CUDD.

#### The Verification Package

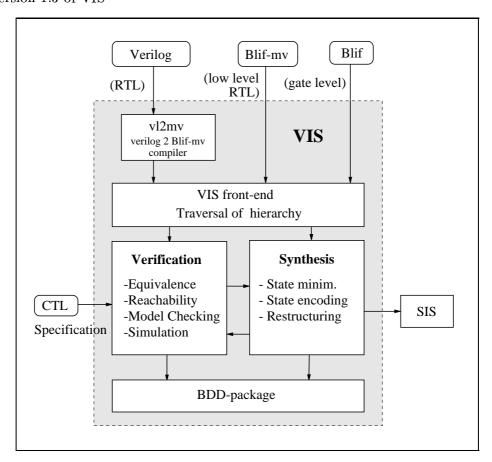

The Verification Interacting with Synthesis Package (VIS) [VIS] is a cooperation of the Carnegie Mellon University, University of California Berkeley and University of Colorado at Boulder. It integrates synthesis, simulation and formal verification of finite state machines. The algorithms for these tasks are based on OBDDs. The interface to the OBDD package is transparent, i. e. independent of the chosen OBDD package. Currently three packages are

supported: CMU [Lon92], CAL [CAL] and CUDD. We are using solely the CUDD package. Figure 1.10 shows the architecture of the VIS system. The VIS front-end is able to read in gate level BLIF (Berkeley Logic Interchange Format) descriptions or low-level RTL descriptions in BLIF-MV [Kuk96]. Together with the vl2mv compiler, which compiles Verilog [TM91] into BLIF-MV, a subset of Verilog at RT-level can be read in. VIS itself implements algorithms for representation, simulation and verification of FSMs. For optimization of FSMs, VIS interacts with SIS (Sequential Interactive Synthesis) [SIS]. We are working with version 1.3 of VIS

Figure 1.10: Architecture of the VIS-system

# Chapter 2

# A Case Study in Formal Verification

In the previous chapter we have learned about two important techniques for the verification of sequential systems in CAD, which are reachability analysis and model checking. In this chapter we will conduct a case study, which presents the application of formal verification methods in an industrial surrounding. We develop a methodology which allows to integrate formal verification in the design flow.

The abilities of formal verification, as well as its limitations become visible. The limitations of the approach motivate the research that is presented in the remaining chapters.

This chapter is structured as follows: In the next section we discuss the application of formal verification in industrial settings and briefly present the synthesis and verification tool Protocol Compiler. The next section presents our formal verification methodology, which is based on assertion checking. The methodology is applied to two examples that are taken from the networking arena. The first is a simplified RS232 transceiver, the second a pipelined FIFO-like buffer written in Verilog. Because the examples represent different types of protocols, two different techniques are given. At the end of the section the general problem of the handling of inputs during verification is discussed. The last section concludes the chapter and gives an outlook on challenges and open problems.

# 2.1 Formal Verification in an Industrial Setting

Recently, usage of complex controller and protocol designs like ATM, Sonet, SDH, etc. as well as their complexity has increased and due to Moore's law [Moo65] we can expect this to continue.

Much design time is spent verifying the design and in practice nearly all of it is done by simulation. But, as the complexity of the design increases, simulation loses its sufficiency. To guarantee correctness of complex designs, formal verification techniques like model checking or theorem proving are a useful supplement to simulation. Unfortunately, formal verification currently does not fit well into the design process for multiple reasons:

- Fairness constraints and specifications must be given in languages such as CTL, that are not related to any hardware description language (HDL), hence unknown by most designers. Also, they are not very intuitive.

- formal verification is an inherently complex task.

- Expert guidance is required.

- When formal verification finds a bug, it is difficult to determine where the bug originates from.

In this case study we present two examples how to apply formal verification methods in Protocol Compiler. We use a simulation-like approach and re-use the testbench for simulation as well as assertion checking.

This case study demonstrates the possibility of integrating formal verification in the design process of real life controllers. Nevertheless, its limitations and challenges become visible. This chapter serves as a motivation for the problems that are addressed in the following chapters.

#### 2.1.1 Protocol Compiler

Protocol Compiler is a design environment for the processing of structured data streams such as the ATM, SDH/SONET, or MPEG protocols. It is based on previous work by Seawright, Brewer, and Crews on logic synthesis from grammatical productions [SB94, CB96]. Seawright gave an overview of the tool [Sea96] and Holtmann and Meyer application examples for SPDIF [HB98] and SDH/SONET [MST97a] protocols. The design environment consists of entry, debugging support, protocol synthesis, and HDL generation (both VHDL [HJ96] and Verilog [TM91] are supported). The Protocol Compiler language is conceptually higher than register transfer level (RTL).

Protocol Compiler provides a sophisticated debugging environment for simulation as well as formal verification based on the following features:

- The high-level language of Protocol Compiler makes it simple to describe stimuli or to check for errors. The language is applicable to the design as well as the testbench.

- Interfaces to Verilog and VHDL simulators are provided.

- Protocol Compiler provides formal verification capabilities like image computation, reachable states computation and model checking [CBM89, Bur90] based on OB-DDs [Bry86]. These formal verification capabilites are set up on the internal representation of the controller, which is also based on OBDDs.

- Results from simulation or formal verification are mapped back onto the source by highlighting frames.

In this case study, we focus on applying assertion checking that is a subproblem of model checking.

## 2.2 An Assertion Checking Methodology for Protocol Compiler

We start the description of our verification methodology by outlining our general verification flow, which closely combines simulation and formal verification. Then, we present two different assertion checking strategies for the verification of two different controllers.

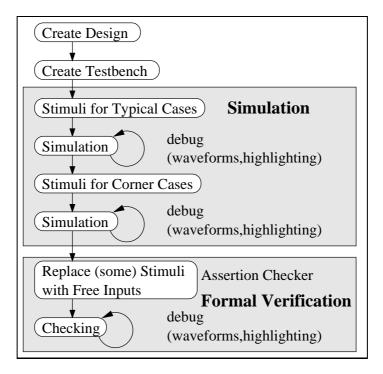

#### 2.2.1 Verification Flow

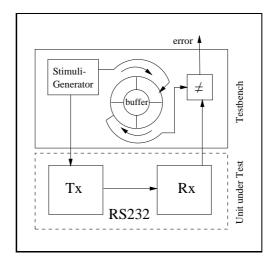

Our design flow (see Figure 2.1) starts with the conventional steps to enter the design, write a testbench and then simulate it and fix bugs. We first check typical cases and then enhance the stimuli generators to cover corner cases as well. During the first cycles of the verification flow it is very likely to have obvious errors that can easily be detected by simulation and do not need the more time consuming formal verification approach.

Figure 2.1: Verification Flow.

In order to cover *all* corner cases we finally apply formal verification in form of assertion checking. Some parts of the stimuli generator are replaced by free inputs but most of the testbench is re-used. An assertion checker is added. Then, the formal verification engine of Protocol Compiler is used.

Assertion checkers are part of the testbench and prove whether the design under test behaves correct, i.e. the correct result is returned. We use the same or similar assertion checkers for simulation and formal verification.

During formal verification, we perform assertion checking by computing all reachable states and determining whether an assertion is violated in any of the states. If a bug is found, i.e. an assertion is violated, we generate a trace file and review it with a waveform viewer. The trace shows the shortest explicit sequence of input values and state transitions leading to the bug.

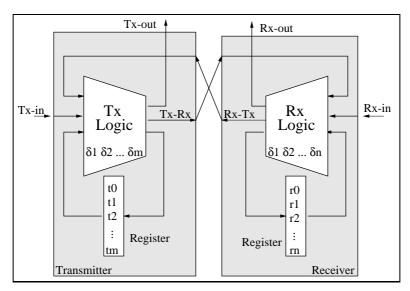

#### 2.2.2 Example RS232

As the first example, we show how to verify a simplified RS232 receiver with simulation and formal verification methods.

The RS232 is a simple and well-known serial communication interface. Transmission is done through a single wire (we ignore all control signals). A byte is transmitted as a sequence of

8 data bits plus some start, stop and parity bits. For the sake of simplicity, we assume that receiver and transmitter are already synchronized at the bit-level. Also, we always use two stop bits and even parity.

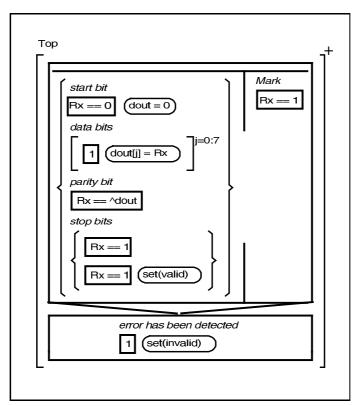

Figure 2.2 shows the implementation of the receiver with Protocol Compiler. Thick outlined boxes are terminal frames and describe a delay of 1 clock cycle plus a condition like Rx==0 to be met. Other frames describe sequence  $\{\ \ \}$ , repetition  $[\ \ ]^+$  or concurrency  $[\ \ ]^+$ . Ovals are actions which are executed whenever the corresponding frame successfully finishes. If the incoming bit stream is invalid, e.g. a wrong parity bit, then the corresponding terminal frame will not accept and the exception frame executes the action set(invalid) for one cycle before the receiver resumes.

Please see the overview [Sea96] or application papers [MST97a, HB98] of Protocol Compiler for a more detailed description of the language.

Figure 2.2: Protocol Compiler Implementation of the RS232 Controller.

All frames of the controller put together work as follows: The Top frame first repeats executing the terminal frame Rx==1 on the right-hand side of the alternative frame until Rx goes to 0. Then execution shifts to the left side and a full word is read, beginning with the start bit Rx==0, 8 data bits, parity and two stop bits. If the parity bit has the wrong value, then the terminal frame Rx==!dout will not accept, thus raising an error and execution jumps into the exception handler at the bottom where the invalid flag is set. Ditto both stop bits are checked. Then, the receiver starts searching for the first start bit (Rx==0) again.

In this example we show how to apply formal verification methods by reusing a major part of the simulation testbench. In other words, how to apply formal verification without leaving the design-simulation track.

We start the verification task with simulation. The simulation is driven by a testbench that creates inputs (e.g., using a counter) and sends them to the Transmitter (Tx) of the RS232.

Furthermore, these messages are buffered in a circular register. The register is needed to store the messages for the latency period between sending and receiving. In this example a register with two slots is sufficient, since only one message is pending at a time. One register is keeping the actual message, the other one is ready for writing. The circular register also allows simultaneous reading and writing. Each time a message is delivered from the Receiver (Rx) it is compared to the actual message in the circular register. The error flag is set, if these messages differ. See Figure 2.3 for a schematic view of the testbench.

Figure 2.3: Schematic View of the Testbench for the RS232.

This setup provides us with a sound testing environment, e.g. we can test the correct transmission of all 256 possible input values. But, this simulation cannot assure full correctness of the controller, since it is not only required to test all possible values, but all possible sequences of input values including any arbitrary number of ready=0 signals in between.

A simulation testbench is not able to process this infinite input stream. If we want to assure correctness over all input sequences we have to use formal verification methods.

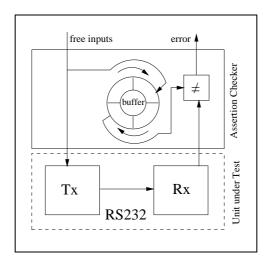

As part of the transformation from simulation to formal verification we build an assertion checker (AC) by reusing most of the testbench. The only change for assertion checking is to remove the stimuli generator from the testbench and to declare the inputs to be free. Free inputs are treated like external inputs, i. e. no special value is assigned and thus the inputs can take any possible value in any clock-cycle. In this context a free input is like a stimuli generator that exhausts all possible sequences of all possible values. After doing this we lose the ability to perform simulation in return for the possibility of assertion checking. Figure 2.4 shows the assertion checker for the RS232.

Assertion checking amounts to computing the set of reachable states. After this set has been computed, checking the correctness property is easy: The situation when an error occurs, i.e., the *error* flag is set, marks a state or a set of states. We only have to check whether the error states are within the reachable state set.

The testbench describes the fairness constraints and specifications necessary for assertion checking. Normally, they would be written in languages such as CTL (see [Bur90]), which are not related to HDLs and unknown by most designers. This is one of the reasons why application of formal verification is currently difficult. Instead of CTL, we use the Protocol Compiler language which is similar to an HDL but at an higher abstraction level. Because the language is fully synthesizable, all constructs can be turned into OBDDs making formal verification possible.

Figure 2.4: Schematic View of the Assertion Checker for the RS232

#### **Experimental Results**

The verification of the RS232 required 34 seconds on a 336 MHz UltraSPARC-II, resulting in 268,545 reachable states within a sequential depth of 29 shells. The design was proven to be correct.

In the next example we present a more sophisticated assertion checking method and show how to combine assertion checking and debugging at the source level.

#### 2.2.3 Example Cow-Stomach

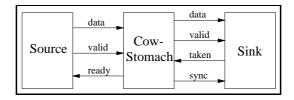

The second example is a "cow-stomach": a small FIFO-like buffer inserted between two modules forming a source and sink. In networking designs, pairs of modules often form a source and sink. In general, data simply flows from source to sink, however the sink is sometimes not able to accept data and indicates this by clearing a ready flag. Common design practice is to register all flags (ports) between modules to improve clock speed. This introduces a one-clock-cycle delay per register, so the sink must indicate with ready that it will be ready in the next cycle to accept data.

The sink essentially has to predict its ability to accept data a cycle later, however, in some designs this is not possible. The best thing the sink can do is to provide a taken flag indicating that is was able to accept data in the current clock cycle. In that case we need to insert a FIFO-like buffer between source and sink. We call this buffer a cow stomach and its goal is to provide maximum throughput using only few resources (see Figure 2.5).

Figure 2.5: Cow-Stomach.

The cow stomach also has registered outputs, so there is now a four cycle delay to send a data token from source to sink and an acknowledgment back. The cow stomach consists of

a buffer, organized as a FIFO, and control logic. We found that designing the control logic, although not too complex, was easy to get wrong. The difficulty arises from the fact that data has to be speculatively send from the source several cycles before it is known whether the sink will accept the data. One can view this as a 2-stage pipeline. The cow-stomach must store up to 4 data tokens, so the controller must also keep track of the buffer status as well as the pipeline stages.

We implemented the cow-stomach as an explicit FSM (Figure 2.6: for simplicity all actions and conditions have been removed) in Verilog and imported it to Protocol Compiler using a prototype Verilog parser.

Figure 2.6: Cow-Stomach Controller.

The cow-stomach represents a common type of design where data is transferred and/or modified. The control is unstructured and depends on many flags. Errors that may occur in this context include:

- Buffer underflow or overflow,

- lost or duplicated messages, and

- out-of-order messages.

Although the control logic has only nine states, the design had initially several errors. For example, the **ready** flag was cleared too late with the result that the source kept on sending data and the internal buffer overflowed later.

To check the controller for these errors, we start with a simulation using a testbench similar to the one used in the previous example. In this case, the circular register has to be larger (at least five slots) due to the higher number of messages buffered.

After a detailed simulation phase, we may assure correctness of the controller for many situations, but again, we cannot assure correctness for all possible situations. At this stage

we could turn the testbench into an assertion checker as in the previous example to check the controller for the errors described above, instead we propose a different method for two reasons:

- 1. The larger circular register and the higher bit-width of the messages may make formal verification of the controller too complex.

- 2. The Cow-Stomach is a *data-independent* protocol which allows us to use a more efficient method for the verification.

A data-independent protocol is a protocol whose control only depends on control inputs (flags like valid or ready), but not on the data itself. The RS232, for example, is data-dependent, since it computes the parity bit from the input. For a detailed analysis of data-independency refer to Wolper [Wol86]. For the verification of data independent protocols no circular register is needed. Since the data does not influence the behavior of a data-independent protocol, the data input width can be reduced to one bit. Wolper has also shown that this bit is sufficient to distinguish messages and we take advantage of this fact.

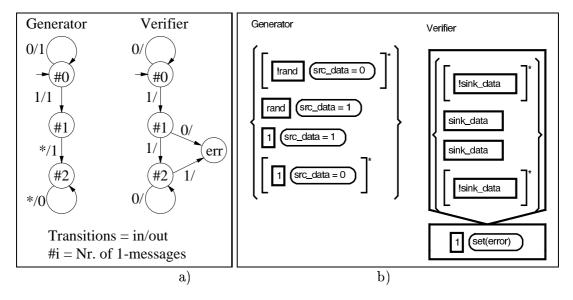

The assertion checker for the verification is built in the following way: The generator part of the assertion checker generates an arbitrary number of 0-messages. Then two consecutive 1-messages are sent, followed by 0-messages. The receiving part of the assertion checker checks whether the output of the protocol fulfills the following properties:

- Exactly two 1-messages are sent, and

- the 1-messages arrive consecutively.

The assertion checker does this symbolically for all streams of 0-messages with two consecutive 1-messages embedded into it. Errors in the design are detected in the following way:

- If a message is lost, there exists a stream for which one 1-message is lost.

- If a message is duplicated, there exists a stream for which one 1-message is duplicated, resulting in three 1-messages.

- If the order of messages is disturbed, there exists a stream where the two 1-messages are no longer consecutively.

If data is corrupted, then there is a stream with either only one or three 1-messages. See Figure 2.7 for a representation of the Assertion Checker.

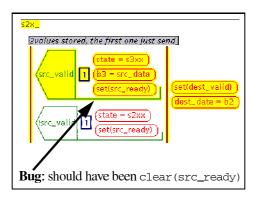

After the cow-stomach passed all simulation tests we still found one more bug with formal verification using this assertion checker.

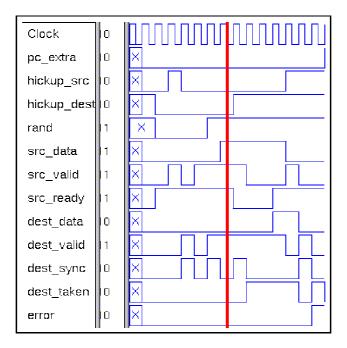

Usually, formal verification confirms that your design works correct but what do you do when it still has bugs? What is needed is a way to explicitly find the conditions under which the error occurs and why. We use Protocol Compiler's facility to trace to a certain state (in this case the error state) to get a shortest path of state transitions to the error state. A trace file is generated and examined with a waveform viewer as shown in Figure 2.8.

We found that being able to see a specific trace leading to an error is very helpful. Protocol Compiler allows to move the marker (the vertical line in the middle of Figure 2.8) backward

Figure 2.7: Assertion Checker a) as FSM b) in Protocol Compiler.

and see which states were executed in the source. We did this and found the cause of the error happened 7 cycles earlier in the state shown in Figure 2.9. The shading indicates which frames and actions were executed in the current clock cycle.

The problem was that the **src\_ready** flag was incorrectly set high too early. Consequently, the source sent more data than the cow-stomach could store and a token was lost.

Using this kind of a assertion checker we add only a small overhead to the design. This allows a fast computation and little memory requirements. Nevertheless, since only one bit of the input data is required for the verification one either should reduce the bit-width of the input to one or at least set the unused bits to default values. This keeps the state space and the sequential depth of the FSM to a minimum.

### **Experimental Results**

We performed the assertion checking of the (correct) cow-stomach protocol on a 336 MHz UltraSPARC-II. It takes 7 seconds to compute the protocol's 1763 reachable states in a sequential depth of 15 shells (includes testbench and assertion checker).

### 2.2.4 Dealing with Inputs during Verification

In preparation of the assertion checker the inputs (i. e. ports) to the design have to be chosen carefully. Each input may belong to one of the three types given below:

- Inputs driven by the assertion checker,

- free inputs, or

- fixed inputs.

All inputs affecting the property that is checked by the assertion checker process have to be driven by the assertion checker. This includes the data-path of the controller as well as timeouts etc.. Assertion checking is conservative regarding the choice of inputs. This means,

Figure 2.8: Diagnostic Trace

Figure 2.9: Discovered Bug

choosing the wrong inputs to be free will introduce false negatives, i. e. probably non-existing errors are notified, but it will never ignore real errors. For example, setting the data-input of the RS232-receiver to a free input will produce an error, due to the arbitrary input values like missing stop bits, although the receiver is error-free.

Any input not affecting the assertion checking process may be set to a free input. The problem that arises from this strategy is that too many free inputs increase the number of reachable states and the sequential depth of the system, making a successful assertion checking problematic. This problem may be avoided by setting inputs to fixed values. But these variables have to be chosen carefully. For example: The cow-stomach has an input hick-up that is set, if the sink has a congestion while processing data. Setting this input in to a fixed value will prevent a meaningful assertion checking. Setting assertion checking-related variables to fixed values may be detected by the fact that fractions of the controller that should be checked are no longer reachable at all (but this is not guaranteed).

Another way to lower the complexity of the assertion checking is to reduce the bandwidth of the data-path-variables. Once a controller has been judged data-independent the width of the data-path may be set to 1. This may be done by fixing the other bits of the data-path

or – preferably – by reducing the bit-width within the protocol's declaration. Within data-dependent protocols reducing the bit-width of the data-path will influence the computation, and thus has to be done very carefully.

### 2.3 Conclusion and Open Problems